You have entered a value in the highlighted fields below that contain invalid characters. Please revise your selection using valid characters only.

Product may not be an exact match for your search

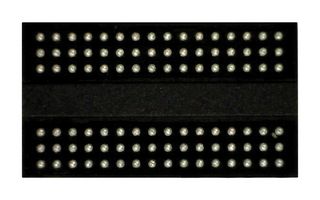

MICRON MT41K512M16VRP-107 IT:P

DRAM, DDR3L, 8 Gbit, 512M x 16bit, 933 MHz, TFBGA, 96 Pins

- Manufacturer:

- MICRON MICRON

- Manufacturer Part No:

- MT41K512M16VRP-107 IT:P

- Order Code:

- 3530740

-

-

Maximum Part Numbers added.

Delete older entries to add more.

- Product Range

- -

- Technical Datasheet:

- MT41K512M16VRP-107 IT:P Datasheet

Product Overview

- Backward compatible to VDD = VDDQ = 1.5V ±0.075V

- Differential bidirectional data strobe, 8n-bit prefetch architecture

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS (READ) latency (CL), programmable posted CAS additive latency (AL)

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Self refresh temperature (SRT), automatic self refresh (ASR), write levelling

- AEC-Q100, PPAP submission, 8D response time

- 96-ball FBGA package

- Industrial temperature range from -40°C ≤ TC ≤ +95°C

- 1.07ns at CL = 13 (DDR3-1866) cycle time, 512 Meg x 16 configuration

Product Information

Want to see similar products? Simply select your required attributes below and hit the button ×

- :

- DDR3L

- :

- 8Gbit

- :

- 512M x 16bit

- :

- 933MHz

- :

- TFBGA

- :

- 96Pins

- :

- 1.35V

- :

- Surface Mount

- :

- -40°C

- :

- 95°C

- :

- -

- :

- MSL 3 - 168 hours

Technical Documents (1)

6,822 In stock Need more?

6,822 deliver in 3-4 business days from our UK warehouse :(UK stock) Order before 17:00 Mon-Fri (excluding National Holidays)

You can reserve stock now just order your desired quantity and checkout as normal. The quantity that cant be dispatched now will be placed on back order and sent as soon as we get a delivery from our supplier. You only get charged when the products are dispatched to you.

Extra stock is available upon order to the Supplier Lead Time which is approximately 7/7/25

Due to market conditions delivery times are for general guidance only and may be subject to change at short notice

Pricing is unavailable. Please contact customer services.

- Price for:

- Each

- 1+

- 10+

| Quantity | Price (Incl JCT) | Your Price (Incl JCT) |

|---|---|---|

| 1+ | ¥2,762.66 (¥3,038.93) | ( ) |

| 10+ | ¥2,634.66 (¥2,898.13) | ( ) |

| Quantity | Price (Incl JCT) | Your Price (Incl JCT) |

|---|

Pricing is unavailable. Please contact customer services.